Всем доброго времени суток! Наблюдал недавно устранение проблемы в одном из проектов, решение там оказалось на поверхности, но поиск занял довольно длительное время, поскольку в первую, во вторую, в третью и в десятую очередь проверялось абсолютно другое (что в принципе казалось логичным). Поэтому решил интереса ради добавить небольшую тестовую рубрику с ситуациями из реальных проектов, возможно кому-то будет интересно и полезно. Переходим к сути вопроса...

Итак, допустим есть схема следующего вида:

Ничего неординарного, все лишнее я вырезал:

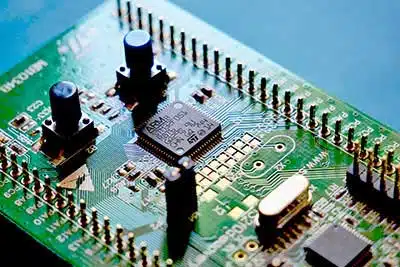

- USB-разъем, с него же идет питание

- LDO-преобразователь, чтобы получить 3.3В

- USB-UART на базе CH340G

- Контроллер STM32F103RC

- Необходимая обвязка и остальное по мелочи

Суммарно имеем:

- U1: STM32F103RCT6

- U2: USBLC6-4SC6

- U3: USBLC6-2SC6

- U4: CH340G

- U5: MCP6001UT-I/OT

- U6: AMS1117-3.3

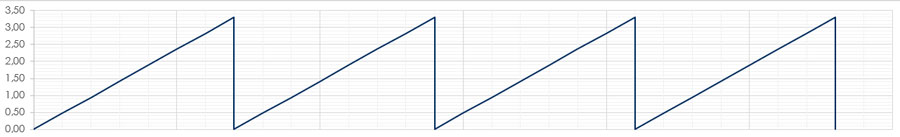

Какая стоит в данном случае задача? А задача крайне простая: ЦАП контроллера (PA4) генерирует пилообразное напряжение с диапазоном от 0 до 3.3В с периодом 100 мс. Графическая интерпретация такая (на выходе DAC STM32):

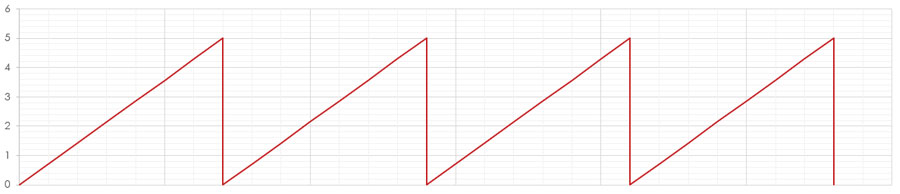

Целью же является получить на выходе (разъем P2) аналогичный сигнал только с диапазоном от 0 до 5В (значения я буду плюс-минус округлять, понятно, что абсолютно без потерь получить сигнал на выходе невозможно):

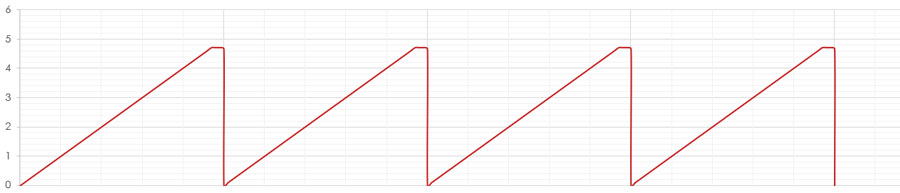

Это все в теории, на практике получается следующее:

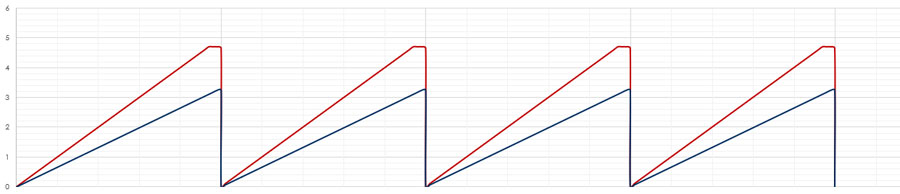

И вместе с сигналом с выхода STM32:

Как видите, начиная с некоторого значения на ЦАП (пусть будет около 3.0 В) увеличение сигнала на выходе прекращается. Вот в общем-то и все, в этом и заключается вопрос - где ошибка?

Давайте резюмируем, ожидание:

| STM32 DAC | Output | STM32 DAC | Output |

|---|---|---|---|

| 0.00 В | 0.00 В | 2.00 В | 3.04 В |

| 0.50 В | 0.75 В | 2.50 В | 3.78 В |

| 1.00 В | 1.51 В | 3.00 В | 4.54 В |

| 1.50 В | 2.27 В | 3.30 В | 5.0 В |

Реальность:

| STM32 DAC | Output | STM32 DAC | Output |

|---|---|---|---|

| 0.00 В | 0.00 В | 2.50 В | 3.78 В |

| 0.50 В | 0.75 В | 3.00 В | 4.5 В |

| 1.00 В | 1.51 В | 3.1 В | 4.5 В |

| 1.50 В | 2.27 В | 3.2 В | 4.5 В |

| 2.00 В | 3.04 В | 3.3 В | 4.5 В |

Неплохая в целом задача, можно пихнуть на какой-нибудь начальный этап собеседования 👍 Если рубрика более-менее зайдет, то можно будет накидать много таких небольших реальных случаев и завести какую-нибудь статистику, рейтинг участвующих в решении, призы, награды, медали, грамоты 😉

Если у кого-то есть идеи, пишите в ЛС, ну либо в комментарии или в группе.

Напряжение на USBLC6-4 (U2, pin 5) составляет 3.3 В, а сигнал на I/O1 может превышать данное значение, что и приводит к наблюдаемому эффекту. Как вариант - ставить еще одну USBLC6-4 исключительно для OPAMP_DAC и кормить ее от 5 В.

Падение напряжения на выходных каскадах операционника. Нужно поднять напряжение питания на 1 вольт?

Привет, не) USBLC6-4, которая U2, к 3.3В подключена, а сигнал-то до 5В может быть, вот через диод и утекает.

Я даже не знаю что это такое.

И посмотреть поленился.

Но мой вариант имеет право на жизнь.

Это да, просто для rail-to-rail 0.5В слишком много, на самом деле я округлил, там что-то около 4.3В чтоли предельное значение, не помню...

уменьшить коэффициент усиления ОУ, самую малость

Данные с преобразованного сигнала подать на цап и ввести подстройку сигнала. То есть ввести обратную связь

Естественно через делитель сигнала, а лучше всего применить внешний стабильный ЦАП. Частота сигнала небольшая, так что подстоиться успеем.